# **Blackfin<sup>®</sup> Embedded Processor**

# **Preliminary Technical Data**

# **ADSP-BF537 Data Sheet Addendum**

#### **FEATURES**

533 and 600 MHz high performance Blackfin processors Two 16-bit MACs, two 40-bit ALUs, four 8-bit video ALUs, 40-bit shifter

RISC-like register and instruction model for ease of programming and compiler-friendly support Advanced debug, trace, and performance monitoring 1.25 V to 1.3 V core V<sub>DD</sub> with on-chip voltage regulation 2.5 V and 3.3 V-compliant I/O with specific 5 V-tolerant pins 182-ball and 208-ball RoHS compliant MBGA packages

#### **MEMORY**

132K bytes of on-chip memory comprised of: Instruction SRAM/cache: instruction SRAM: data SRAM/cache; additional dedicated data SRAM; scratchpad SRAM

External memory controller with glueless support for SDRAM and asynchronous 8-bit and 16-bit memories Flexible booting options from external flash, SPI® and TWI memory or from SPI, TWI, and UART host devices Memory management unit providing memory protection

#### **PERIPHERALS**

Debug/JTAG interface

IEEE 802.3-compliant 10/100 Ethernet MAC Controller area network (CAN) 2.0B interface Parallel peripheral interface (PPI), supporting ITU-R 656 video data formats

Two dual-channel, full-duplex synchronous serial ports

(SPORTs), supporting eight stereo I<sup>2</sup>S channels 12 peripheral DMAs, 2 mastered by the Ethernet MAC Two memory-to-memory DMAs with external request lines **Event handler with 32 interrupt inputs** Serial peripheral interface (SPI)-compatible Two UARTs with IrDA® support Two-wire interface (TWI) controller Eight 32-bit timer/counters with PWM support Real-time clock (RTC) and watchdog timer 32-bit core timer 48 general-purpose I/Os (GPIOs), 8 with high current drivers On-chip PLL capable of 0.5× to 64× frequency multiplication

## GENERAL DESCRIPTION

This data sheet addendum introduces several new ADSP-BF537 models. Supported by revision 0.3 silicon, these new models will not be offered with previous revisions of ADSP-BF537 silicon. These new models are also offered as x-grade. Please see Ordering Guide on Page 6.

Blackfin and the Blackfin logo are registered trademarks of Analog Devices, Inc.

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

©2007 Analog Devices, Inc. All rights reserved.

### **SPECIFICATIONS**

Note that component specifications are subject to change without notice.

#### **OPERATING CONDITIONS**

| Param                | eter                                                          |                                                                                                                   | Min  | Nominal | Max   | Unit |

|----------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------|---------|-------|------|

| V <sub>DDINT</sub>   | Internal Supply Voltage <sup>1</sup>                          | @ 533 MHz                                                                                                         | 1.20 | 1.25    | 1.375 | V    |

| $V_{\text{DDINT}}$   | Internal Supply Voltage <sup>1</sup>                          | @ 600 MHz                                                                                                         | 1.30 | 1.30    | 1.43  | V    |

| $V_{\text{DDEXT}}$   | External Supply Voltage                                       |                                                                                                                   | 2.25 | 3.3     | 3.6   | V    |

| $V_{DDRTC}$          | Real Time Clock Power<br>Supply Voltage                       |                                                                                                                   | 2.25 |         | 3.6   | V    |

| $V_{IH}$             | High Level Input Voltage <sup>2, 3</sup>                      | @ V <sub>DDEXT</sub> = Maximum                                                                                    | 2.0  |         | 3.6   | V    |

| $V_{\text{IHCLKIN}}$ | High Level Input Voltage <sup>4</sup>                         | @ V <sub>DDEXT</sub> = Maximum                                                                                    | 2.2  |         | 3.6   | V    |

| $V_{\text{IH5V}}$    | 5.0 V Tolerant Pins, High<br>Level Input Voltage <sup>5</sup> | $@V_{DDEXT} = Maximum$                                                                                            | 2.0  |         | 5.5   | V    |

| $V_{IL}$             | Low Level Input Voltage <sup>2, 6</sup>                       | @ V <sub>DDEXT</sub> = Minimum                                                                                    | -0.3 |         | +0.6  | V    |

| $V_{\text{IL5V}}$    | 5.0 V Tolerant Pins, Low<br>Level Input Voltage⁵              | $@V_{DDEXT} = Minimum$                                                                                            | -0.3 |         | +0.8  | V    |

| TJ                   | Junction Temperature                                          | 208-Ball Chip Scale Ball Grid Array (CSP-BGA) @ $T_{AMBIENT} = -40^{\circ}C$ to $+85^{\circ}C$                    | -40  |         | +105  | °C   |

| TJ                   | Junction Temperature                                          | 208-Ball Chip Scale Ball Grid Array (CSP-BGA) @ $T_{AMBIENT} = 0^{\circ}C$ to $+70^{\circ}C$                      | -40  |         | +105  | °C   |

| TJ                   | Junction Temperature,                                         | 182-Ball Chip Scale Ball Grid Array (CSP-BGA) @ $T_{AMBIENT} = -40^{\circ}C$ to $+85^{\circ}C$                    | -40  |         | +105  | °C   |

| T <sub>J</sub>       | Junction Temperature,                                         | 182-Ball Chip Scale Ball Grid Array (CSP-BGA) @ $T_{\text{AMBIENT}} = 0^{\circ}\text{C}$ to $+70^{\circ}\text{C}$ | -40  |         | +105  | °C   |

$<sup>^1</sup>$  The regulator generates  $V_{\mathrm{DDINT}}$  levels from 0.85 V to 1.2 V with -5% to +10% tolerance and a level of 1.25 V with -4% to +10% tolerance. For 600 MHz models only, the regulator generates a level of 1.3 V with 0% to +10% tolerance.

<sup>&</sup>lt;sup>2</sup> Bidirectional pins (DATA15–0, PF15–0, PG15–0, PH15–0, TFS0, TSCLK0, RSCLK0, RFS0, MDIO) and input pins (BR, ARDY, DR0PRI, DR0SEC, RTXI, TCK, TDI, TMS, TRST, CLKIN, RESET, NMI, and BMODE2–0) of the ADSP-BF534/ADSP-BF536/ADSP-BF537 are 3.3 V-tolerant (always accept up to 3.6 V maximum V<sub>IH</sub>). Voltage compliance (on outputs, V<sub>OH</sub>) is limited by the V<sub>DDEXT</sub> supply voltage.

<sup>&</sup>lt;sup>3</sup> Parameter value applies to all input and bidirectional pins except CLKIN, SDA, and SCL.

<sup>&</sup>lt;sup>4</sup> Parameter value applies to CLKIN pin only.

$<sup>^5</sup>$  Pins SDA, SCL, and PJ4 are 5.0 V tolerant (always accept up to 5.5 V maximum  $V_{IH}$ ). Voltage compliance (on outputs,  $V_{OH}$ ) is limited by the  $V_{DDEXT}$  supply voltage.

<sup>&</sup>lt;sup>6</sup> Parameter value applies to all input and bidirectional pins except SDA and SCL.

### **ELECTRICAL CHARACTERISTICS**

| Parameter                                                              | Description                                 | Test Conditions                                                                    | Min                      | Max  | Unit |

|------------------------------------------------------------------------|---------------------------------------------|------------------------------------------------------------------------------------|--------------------------|------|------|

| V <sub>OH</sub> (All Outputs and I/Os Except                           | High Level Output Voltage <sup>1</sup>      |                                                                                    | V <sub>DDEXT</sub> - 0.5 |      | ٧    |

| Port F, Port G, Port H)                                                |                                             | @ $V_{DDEXT} = 2.5 \text{ V} \pm 10\%$ , $I_{OH} = -0.5 \text{ mA}$                | V <sub>DDEXT</sub> – 0.5 |      | V    |

| V <sub>OH</sub> (Port F7–0)                                            |                                             | @ $V_{DDEXT} = 3.3 \text{ V} \pm 10\%$ , $I_{OH} = -8 \text{ mA}$                  | $V_{DDEXT} - 0.5$        |      | V    |

|                                                                        |                                             | @ $V_{DDEXT} = 2.5 \text{ V} \pm 10\%$ , $I_{OH} = -6 \text{ mA}$                  | $V_{DDEXT} - 0.5$        |      | V    |

| V <sub>OH</sub> (Port F15–8, Port G, Port H)                           |                                             | $I_{OH} = -2 \text{ mA}$                                                           | V <sub>DDEXT</sub> – 0.5 |      | V    |

| I <sub>OH</sub> (Max Combined for<br>Port F7–0)                        |                                             | $V_{OH} = V_{DDEXT} - 0.5 \text{ V Min}$                                           |                          | -64  | mA   |

| I <sub>OH</sub> (Max Total for All Port F,<br>Port G, and Port H Pins) |                                             | $V_{OH} = V_{DDEXT} - 0.5 \text{ V Min}$                                           |                          | -144 | mA   |

| V <sub>OL</sub> (All Outputs and I/Os Except                           | Low Level Output Voltage <sup>1</sup>       | @ $V_{DDEXT} = 3.3 \text{ V} \pm 10\%$ , $I_{OL} = 2.0 \text{ mA}$                 |                          | 0.4  | V    |

| Port F, Port G, Port H)                                                |                                             | @ $V_{DDEXT} = 2.5 \text{ V} \pm 10\%$ , $I_{OL} = 2.0 \text{ mA}$                 |                          |      |      |

| V <sub>OL</sub> (Port F7–0)                                            |                                             | @ $V_{DDEXT} = 3.3 \text{ V} \pm 10\%$ , $I_{OL} = 8 \text{ mA}$                   |                          | 0.5  | V    |

|                                                                        |                                             | @ $V_{DDEXT} = 2.5 \text{ V} \pm 10\%$ , $I_{OL} = 6 \text{ mA}$                   |                          | 0.5  | V    |

| V <sub>OL</sub> (Port F15–8, Port G, Port H)                           |                                             | $I_{OL} = 2 \text{ mA}$                                                            |                          | 0.5  | V    |

| I <sub>OL</sub> (Max Combined for Port F7–0)                           |                                             | $V_{OL} = 0.5 \text{ V Max}$                                                       |                          | 64   | mA   |

| $I_{OL}$ (Max Total for All Port F, Port G, and Port H Pins)           |                                             | V <sub>OL</sub> = 0.5 V Max                                                        |                          | 144  | mA   |

| I <sub>IH</sub>                                                        | High Level Input Current <sup>2</sup>       | @ $V_{DDEXT} = 3.6 \text{ V}, V_{IN} = 3.6 \text{ V}$                              |                          | 10   | μΑ   |

| I <sub>IH5V</sub>                                                      | High Level Input Current <sup>3</sup>       | @ $V_{DDEXT} = 3.0 \text{ V}, V_{IN} = 5.5 \text{ V}$                              |                          | 10   | μΑ   |

| I <sub>IL</sub>                                                        | Low Level Input Current <sup>2</sup>        | @ $V_{DDEXT} = 3.6 \text{ V}, V_{IN} = 0 \text{ V}$                                |                          | 10   | μΑ   |

| I <sub>IHP</sub>                                                       | High Level Input Current<br>JTAG⁴           | $@V_{DDEXT} = 3.6 \text{ V}, V_{IN} = 3.6 \text{ V}$                               |                          | 50.0 | μΑ   |

| I <sub>OZH</sub>                                                       | Three-State Leakage<br>Current <sup>5</sup> | $@V_{DDEXT} = 3.6 \text{ V}, V_{IN} = 3.6 \text{ V}$                               |                          | 10   | μΑ   |

| I <sub>OZH5V</sub>                                                     | Three-State Leakage<br>Current <sup>6</sup> | $@V_{DDEXT} = 3.0 \text{ V}, V_{IN} = 5.5 \text{ V}$                               |                          | 10   | μΑ   |

| I <sub>OZL</sub>                                                       | Three-State Leakage<br>Current <sup>5</sup> | $@V_{DDEXT} = 3.6 \text{ V, } V_{IN} = 0 \text{ V}$                                |                          | 10   | μΑ   |

| C <sub>IN</sub>                                                        | Input Capacitance <sup>7,8</sup>            | $f_{IN} = 1 \text{ MHz}, T_{AMBIENT} = 25^{\circ}\text{C}, V_{IN} = 2.5 \text{ V}$ |                          | 8    | рF   |

<sup>&</sup>lt;sup>1</sup> Applies to output and bidirectional pins. <sup>2</sup> Applies to input pins.

<sup>&</sup>lt;sup>3</sup> Applies to input pin PJ4. <sup>4</sup> Applies to JTAG input pins (TCK, TDI, TMS, TRST).

<sup>&</sup>lt;sup>5</sup> Applies to three-statable pins. <sup>6</sup> Applies to bidirectional pins PJ2 and PJ3.

<sup>&</sup>lt;sup>7</sup> Applies to all signal pins.

<sup>&</sup>lt;sup>8</sup> Guaranteed, but not tested.

#### **ABSOLUTE MAXIMUM RATINGS**

Stresses greater than those listed below may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions greater than those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameter                                            | Rating                                               |

|------------------------------------------------------|------------------------------------------------------|

| Internal (Core) Supply Voltage (V <sub>DDINT</sub> ) | -0.3 V to +1.43 V                                    |

| External (I/O) Supply Voltage (V <sub>DDEXT</sub> )  | -0.3 V to +3.8 V                                     |

| Input Voltage                                        | -0.5 V to +3.6 V                                     |

| Input Voltage <sup>1</sup>                           | -0.5 V to +5.5 V                                     |

| Output Voltage Swing                                 | $-0.5 \text{ V to V}_{\text{DDEXT}} + 0.5 \text{ V}$ |

| Load Capacitance <sup>2</sup>                        | 200 pF                                               |

| Storage Temperature Range                            | -65°C to +150°C                                      |

| Junction Temperature Underbias                       | +125°C                                               |

<sup>&</sup>lt;sup>1</sup> Applies to 5 V tolerant pins SCL, SDA, and PJ4.

#### **PACKAGE INFORMATION**

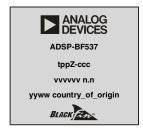

The information presented in Figure 1 and Table 1 provide details about the package branding for the Blackfin processors. For a complete listing of product availability, see Ordering Guide on Page 6.

Figure 1. Product Information on Package

**Table 1. Package Brand Information**

| -         | 1                  |  |

|-----------|--------------------|--|

| Brand Key | Field Description  |  |

| t         | Temperature Range  |  |

| рр        | Package Type       |  |

| Z         | RoHS Compliant     |  |

| ccc       | See Ordering Guide |  |

| VVVVV     | Assembly Lot Code  |  |

| n.n       | Silicon Revision   |  |

| yyww      | Date Code          |  |

$<sup>^2</sup>$  For proper SDRAM controller operation, the maximum load capacitance is 50 pF (at 3.3 V) or 30 pF (at 2.5 V) for ADDR19–1, DATA15–0, ABE1–0/SDQM1–0, CLKOUT, SCKE, SA10, SRAS, SCAS, SWE, and SMS.

#### **TIMING SPECIFICATIONS**

Table 2 and Table 3 describe the timing requirements for the ADSP-BF537 processor clocks. Take care in selecting MSEL, SSEL, and CSEL ratios so as not to exceed the maximum core clock and system clock.

Table 2. Core Clock Requirements—600 MHz Speed Grades<sup>1</sup>

|                   |                                                             |                            | $T_{\text{JUNCTION}} \! \leq 105^{\circ} C^2$ |      |

|-------------------|-------------------------------------------------------------|----------------------------|-----------------------------------------------|------|

| Parameter         |                                                             | Internal Regulator Setting | Max                                           | Unit |

| $f_{\text{CCLK}}$ | Core Clock Frequency (V <sub>DDINT</sub> = 1.3 V Minimum)   | 1.3 V                      | 600                                           | MHz  |

| $f_{\text{CCLK}}$ | Core Clock Frequency (V <sub>DDINT</sub> = 1.20 V Minimum)  | 1.25 V                     | 533                                           | MHz  |

| $f_{\text{CCLK}}$ | Core Clock Frequency (V <sub>DDINT</sub> = 1.14 V Minimum)  | 1.20 V                     | 500                                           | MHz  |

| $f_{\text{CCLK}}$ | Core Clock Frequency (V <sub>DDINT</sub> = 1.045 V Minimum) | 1.10 V                     | 444                                           | MHz  |

| $f_{\text{CCLK}}$ | Core Clock Frequency (V <sub>DDINT</sub> = 0.95 V Minimum)  | 1.00 V                     | 400                                           | MHz  |

| $f_{\text{CCLK}}$ | Core Clock Frequency (V <sub>DDINT</sub> = 0.85 V Minimum)  | 0.90 V                     | 333                                           | MHz  |

| $f_{CCLK}$        | Core Clock Frequency (V <sub>DDINT</sub> = 0.80 V Minimum)  | 0.85 V                     | 250                                           | MHz  |

$<sup>^1</sup>$ The speed grade of a given part is printed on the chip's package as shown in Figure 1 on Page 4 and can also be seen on the specific products ordering guide. It designates the maximum allowed CCLK frequency at  $V_{DDINT} = 1.3 \text{ V}$  and the maximum allowed VCO frequency at any supply voltage.

Table 3. Core Clock Requirements—533 MHz Speed Grades<sup>1</sup>

|                   |                                                             |                            | $T_{\text{JUNCTION}} \! \leq 105^{\circ}\text{C}^{2}$ |      |

|-------------------|-------------------------------------------------------------|----------------------------|-------------------------------------------------------|------|

| Parameter         |                                                             | Internal Regulator Setting | Max                                                   | Unit |

| $f_{\text{CCLK}}$ | Core Clock Frequency (V <sub>DDINT</sub> = 1.2 V Minimum)   | 1.25 V                     | 533                                                   | MHz  |

| $f_{\text{CCLK}}$ | Core Clock Frequency (V <sub>DDINT</sub> = 1.14 V Minimum)  | 1.20 V                     | 500                                                   | MHz  |

| $f_{\text{CCLK}}$ | Core Clock Frequency (V <sub>DDINT</sub> = 1.045 V Minimum) | 1.10 V                     | 444                                                   | MHz  |

| $f_{\text{CCLK}}$ | Core Clock Frequency (V <sub>DDINT</sub> = 0.95 V Minimum)  | 1.00 V                     | 400                                                   | MHz  |

| $f_{\text{CCLK}}$ | Core Clock Frequency (V <sub>DDINT</sub> = 0.85 V Minimum)  | 0.90 V                     | 333                                                   | MHz  |

| $f_{CCLK}$        | Core Clock Frequency (V <sub>DDINT</sub> = 0.80 V Minimum)  | 0.85 V                     | 250                                                   | MHz  |

$<sup>^1</sup>$ The speed grade of a given part is printed on the chip's package as shown in Figure 1 on Page 4 and can also be seen on the specific products ordering guide. It designates the maximum allowed CCLK frequency at  $V_{\rm DDINT} = 1.25~{

m V}$  and the maximum allowed VCO frequency at any supply voltage.

<sup>&</sup>lt;sup>2</sup> See Operating Conditions on Page 2.

<sup>&</sup>lt;sup>2</sup> See Operating Conditions on Page 2.

#### **ORDERING GUIDE**

| Model                           | Temperature<br>Range <sup>1</sup> | Speed Grade<br>(Max) | Operating Voltage (Nominal) | Package Description     | Package<br>Option |

|---------------------------------|-----------------------------------|----------------------|-----------------------------|-------------------------|-------------------|

| ADSP-BF537BBCZ-5AV <sup>2</sup> | -40°C to +85°C                    | 533 MHz              | 1.25 V internal, 3.3 V I/O  | 182-Ball CSP-BGA        | BC-182            |

| ADSP-BF537BBCZ-5BV <sup>2</sup> | -40°C to +85°C                    | 533 MHz              | 1.25 V internal, 3.3 V I/O  | 208-Ball Sparse CSP-BGA | BC-208-3          |

| ADSP-BF537KBCZ-6AV <sup>2</sup> | 0°C to +70°C                      | 600 MHz              | 1.3 V internal, 3.3 V I/O   | 182-Ball CSP-BGA        | BC-182            |

| ADSP-BF537KBCZ-6BV <sup>2</sup> | 0°C to +70°C                      | 600 MHz              | 1.3 V internal, 3.3 V I/O   | 208-Ball Sparse CSP-BGA | BC-208-3          |

$<sup>^{\</sup>rm l}$  Referenced temperature is ambient temperature.

<sup>&</sup>lt;sup>2</sup> Z = RoHS compliant part.